## University of South Florida Scholar Commons

Graduate Theses and Dissertations

Graduate School

June 2018

# Development of 3-D Printed Hybrid Packaging for GaAs-MEMS Oscillators based on Piezoelectrically-Transduced ZnO-on-SOI Micromechanical Resonators

Di Lan University of South Florida, dilan@mail.usf.edu

Follow this and additional works at: https://scholarcommons.usf.edu/etd Part of the <u>Electrical and Computer Engineering Commons</u>

## Scholar Commons Citation

Lan, Di, "Development of 3-D Printed Hybrid Packaging for GaAs-MEMS Oscillators based on Piezoelectrically-Transduced ZnOon-SOI Micromechanical Resonators" (2018). *Graduate Theses and Dissertations*. https://scholarcommons.usf.edu/etd/7690

This Dissertation is brought to you for free and open access by the Graduate School at Scholar Commons. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of Scholar Commons. For more information, please contact scholarcommons@usf.edu.

## Development of 3-D Printed Hybrid Packaging for GaAs-MEMS Oscillators based on

Piezoelectrically-Transduced ZnO-on-SOI Micromechanical Resonators

by

Di Lan

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy Department of Electrical Engineering College of Engineering University of South Florida

> Major Professor: Jing Wang, Ph.D. Thomas M. Weller, Ph.D. Arash Takshi, Ph.D. Rasim Guldiken, Ph.D. Shengqian Ma, Ph.D.

> > Date of Approval: June 14, 2018

Keywords: Microelectromechanical Systems, Additive Manufacturing, MMIC, Microfabrication

Copyright © 2018, Di Lan

www.manaraa.com

## DEDICATION

To my wife, my parents, my advisors, my friends

www.manaraa.com

## ACKNOWLEDGMENTS

First, I would like to state my greatest appreciation to my major advisor and Professor Dr. Jing Wang for always providing his guidance on my academic research, mentoring on my professional career, giving me recommendations and supporting me on scholarships. It has been a great and valuable experience to learn from him and work with him for the past six years. I would like to extend my appreciation to Dr. Thomas Weller for giving me the opportunity to work on 3-D Printing projects and providing me with helpful advice on research.

I would like to thank Dr. Larry Dunleavy for recruiting me as an RF Engineering intern at Modelithics, which gave me invaluable industrial experience and opportunities to polish my skill for my research and work. I feel very grateful to work with all the staffs and engineers at Modelithics. Special thanks are given to Scott Skidmore, Kevin Kellogg, Laura Levesque, Adam Furman and Hugo Morales, who have trained me and helped me substantially in my work.

I would like to greatly acknowledge the contributions from current and former group members of RF MEMS Transducers Group, NREC staffs, and all research colleagues of the WAMI Center, especially I-Tsang Wu, Julio Dewdney, Juan Castro, Ivan Rivera, Eduardo Rojas, Enrique Gonzalez and Ting-Hung Liu. I specially thank Xu Han and Adrian Avila for helping me in every aspect of daily school life and spending time on MEMS fabrication in the cleanroom for countless days and nights; Ramiro Ramize for working together on 3-D printing; and Rich Everly for providing assistance in cleanroom training and fabrication techniques.

I would like to express my sincere gratitude to my former advisor Dr. Jiang Hao who enlightened and encouraged me to further pursue my higher education and my parents for supporting and taking care of me for my entire life.

I would like to recognize Qorvo, the former TriQuint Semiconductor, for their complementary foundry services and technical support. I gratefully acknowledge the generous support from II-VI Incorporated on this project.

Last and most importantly, I would like to express my deepest thanks to my wife Yilu Ning Lan who shares happiness and love in every moment of my life. Her support keeps me motivated and moving forward. She is my inspiration to become a better person every day.

## **TABLE OF CONTENTS**

| LIST OF TABLES                                                              | iii    |

|-----------------------------------------------------------------------------|--------|

| LIST OF FIGURES                                                             | iv     |

| ABSTRACT                                                                    | xi     |

| CHAPTER 1: INTRODUCTION                                                     | 1      |

| 1.1 Overview                                                                | 1      |

| 1.2 Review of MEMS Integration                                              | 2      |

| 1.2.1 CMOS-MEMS Integration                                                 | 2<br>2 |

| 1.2.2 Wafer Level Packaging (WLP) and System in Package (SiP)               | 4      |

| 1.3 Current State of the Art MEMS-Based Oscillators                         | 7      |

| 1.3.1 Monolithic CMOS-MEMS Oscillators                                      | 7      |

| 1.3.2 Piezoelectric AlN-Based CMOS Oscillators                              | 9      |

| 1.3.3 MEMS-Based GaN Oscillators                                            | 11     |

| 1.3.4 Drawbacks of the Current State-of-the-Art Technology                  | 11     |

| 1.4 Dissertation Organization                                               | 12     |

| 1.5 Contributions                                                           | 13     |

| CHAPTER 2: BACKGROUND                                                       | 15     |

| 2.1 Piezoelectric Effect                                                    | 15     |

| 2.2 Mathematical Formation for Piezoelectric Effect                         | 16     |

| 2.3 Piezoelectric Materials                                                 | 18     |

| 2.4 Piezoelectrically-Transduced MEMS Resonator and Vibrational Modes       | 20     |

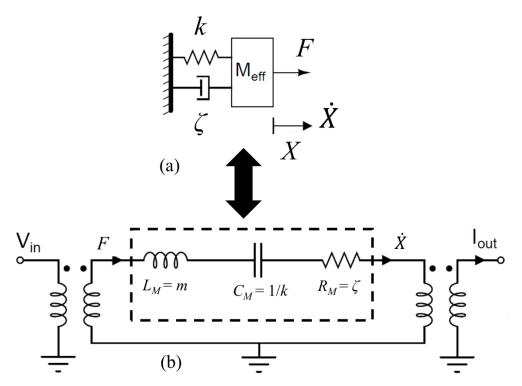

| 2.5 Electrical Circuit Representation of a MEMS Resonator                   | 25     |

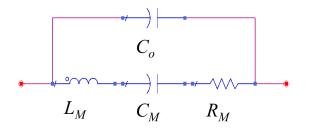

| 2.6 Butterworth-Van Dyke (BVD) Circuit Model                                | 27     |

| CHAPTER 3: DEVELOPMENT OF ZNO THIN-FILM PIEZOELECTRICALLY-                  |        |

| TRANSDUCED RESONATOR                                                        | 30     |

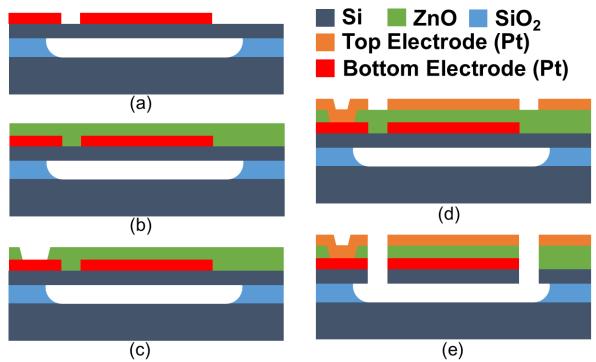

| 3.1 Fabrication Process of ZnO Piezoelectric Resonator on Silicon-on-       | • •    |

| Insulator Wafer                                                             | 30     |

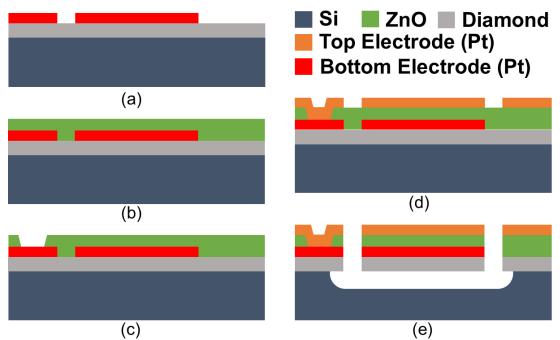

| 3.2 Fabrication Process of ZnO Piezoelectric Resonator on Diamond-on-       |        |

| Silicon Wafer                                                               | 32     |

| 3.3 Simulation of ZnO Thin-film Piezoelectric-on-Substrate (TPoS) Resonator | 33     |

| 3.4 Experimental Results of ZnO TPoS Resonator                              | 36     |

| 3.4.1 Contour Modes in TPoS Resonators                                      | 36     |

| 3.4.2 Comparison of Measurement and Simulation Results                      | 42     |

| 3.4.3 Temperature Dependence                                                | 47     |

| 3.5 Circuit Model of RF Probe Pads and Microstrip Lines on Silicon-on-<br>Insulator and Diamond-on-Silicon Substrates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 51                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| <ul> <li>CHAPTER 4: MEMS-BASED OSCILLATOR DESIGN USING A ZNO-ON-SOI RESONATOR</li> <li>4.1 Equivalent Electrical Circuit Model Extraction for Circuit Simulation</li> <li>4.2 MEMS-Based Oscillator Design</li> <li>4.3 Dual-Frequency MEMS-Based Oscillator Results</li> <li>4.4 MEMS-Based Oscillator Phase Noise</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 57<br>58<br>61<br>64<br>66                                                       |

| <ul> <li>CHAPTER 5: 3-D PRINTED HYBRID PACKAGING USING ADDITIVE<br/>MANUFACTURING AND LASER MACHINING</li> <li>5.1 DPAM and Laser Machined Package Fabrication Process</li> <li>5.1.1 Fused Deposition of Substrate</li> <li>5.1.2 Laser Trimmed RF Feedline and DC Biasing Line</li> <li>5.1.3 Laser Micro-Machined Cavity</li> <li>5.1.4 Laser Micro-Machined Probe Pads and Interconnects</li> <li>5.2 Equivalent Circuit Model of 3-D Printed Probe Pads</li> <li>5.3 Laser Trimming Enhanced Microstrip Line</li> <li>5.3.1 50 Ω Microstrip Line with Laser Trimming</li> <li>5.3.2 Propagation Constant Calculation</li> <li>5.4 3-D Printed Hybrid Packaging</li> <li>5.4.1 Integration of Multiple ICs</li> <li>5.4.2 Integration of Surface-Mount Technology (SMT) Components</li> <li>5.5 Humidity and Temperature Cycling</li> </ul> | 70<br>71<br>72<br>72<br>73<br>74<br>76<br>78<br>78<br>79<br>80<br>81<br>83<br>85 |

| CHAPTER 6: CONCLUSIONS AND FUTURE WORK<br>6.1 Conclusions<br>6.2 Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 88<br>88<br>90                                                                   |

| REFERENCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 93                                                                               |

| APPENDIX A: COPYRIGHT PERMISSIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 100                                                                              |

| APPENDIX B: DETAILED FABRICATION PROCESS FOR ZNO RESONATORS<br>ON SILICON WAFER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 101                                                                              |

| APPENDIX C: DETAILED FABRICATION PROCESS FOR ZNO RESONATORS<br>ON SILICON-ON-INSULATOR WAFER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5<br>106                                                                         |

| APPENDIX D: DETAILED FABRICATION PROCESS FOR ZNO RESONATORS<br>ON DIAMOND-ON-SILICON WAFER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 112                                                                              |

| APPENDIX E: GAAS DISTRIBUTED LOW-NOISE AMPLIFIER DETAIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 117                                                                              |

| ABOUT THE AUTHOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | END PAGE                                                                         |

ii

## LIST OF TABLES

| Table 2.1 | Properties of the most commonly used piezoelectric materials [30-32]                            | 19 |

|-----------|-------------------------------------------------------------------------------------------------|----|

| Table 2.2 | Analogy between electrical and mechanical domain                                                | 27 |

| Table 3.1 | Material properties for the resonator body                                                      | 34 |

| Table 3.2 | Comparison of measurement and FEM simulation results for various designs of ZnO TPoS resonators | 46 |

| Table 3.3 | All parameters of the equivalent circuit model                                                  | 53 |

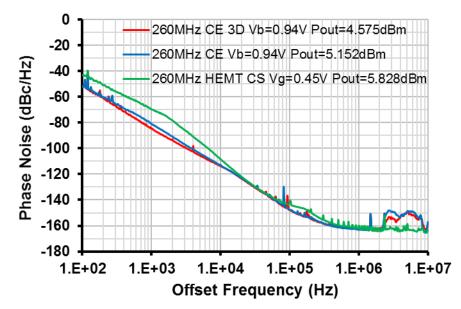

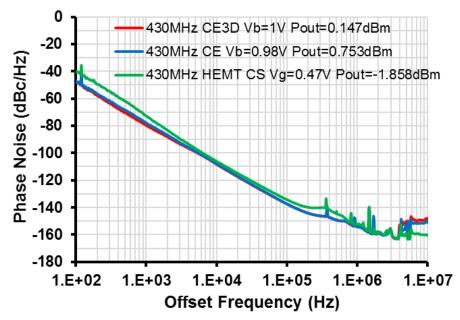

| Table 4.1 | Phase noise performance comparison of all three oscillators                                     | 69 |

## LIST OF FIGURES

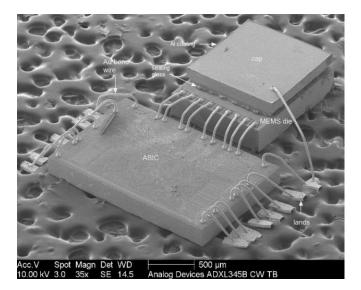

| Figure 1.1  | A SEM image of a MEMS die wirebonded to a CMOS chip through a hybrid modular integration                                                                                                                                                                                                                                                                                                                                                                         | 3  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

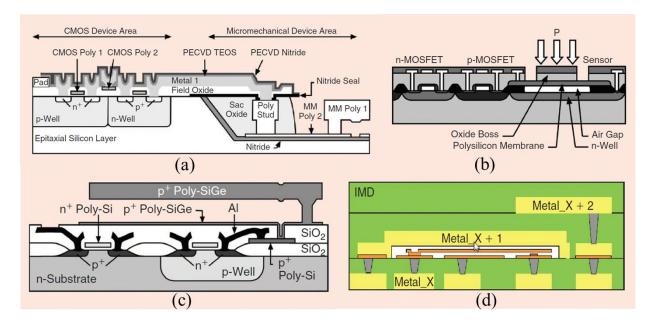

| Figure 1.2  | Cross-sectional schematic diagrams of (a) an integrated CMOS-MEMS<br>chip illustrating the well-known approach by Sandia National Lab [9];<br>(b) Infineon Technologies' integrated MEMS technology for the<br>fabrication of pressure sensors [10]; (c) poly-SiGe microstructure<br>fabricated by post-CMOS surface micromachining techniques on top<br>of a completed CMOS substrate wafer [11]; and (d) a Nanomech<br>MEMS embedded in the CMOS back end [12] | 4  |

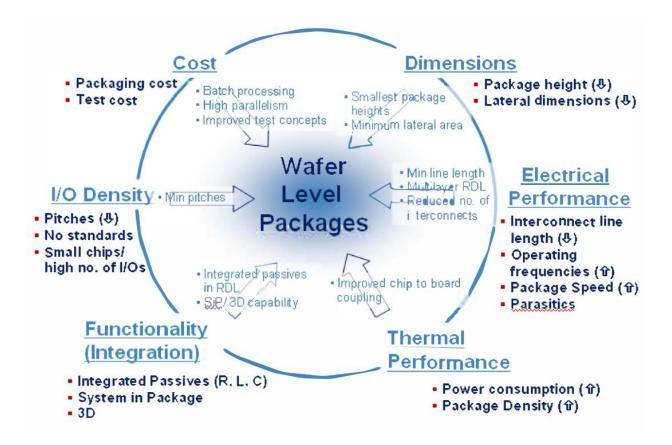

| Figure 1.3  | Driving force for wafer level packaging [13]                                                                                                                                                                                                                                                                                                                                                                                                                     | 5  |

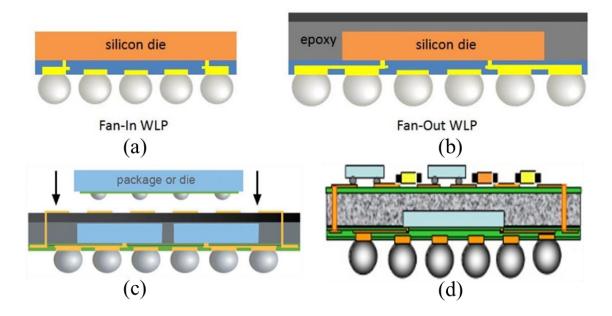

| Figure 1.4  | Conceptual schematic diagrams illustrating (a) eWLB (FI-WLP);<br>(b) eWLB (FO-WLP); (c) Package-on-package (PoP) using double-side<br>eWLB packaging [13]; and (d) System-on-Wafer (SoW) using double-<br>side eWLB packaging [16]                                                                                                                                                                                                                               | 6  |

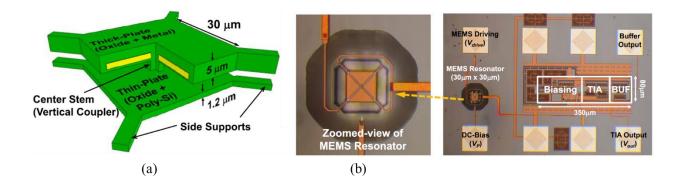

| Figure 1.5  | (a) Perspective view of the vertically-coupled resonator; (b) Optical photos of the CMOS-MEMS resonator oscillator [17]                                                                                                                                                                                                                                                                                                                                          | 8  |

| Figure 1.6  | (a) Magnitude and phase responses of the proposed resonator; (b) Phase noise performance comparison [17]                                                                                                                                                                                                                                                                                                                                                         | 8  |

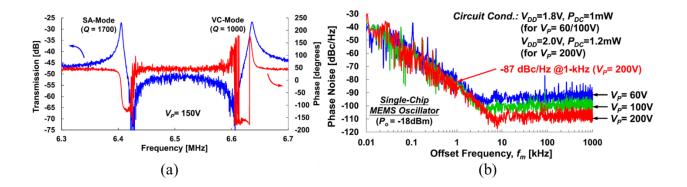

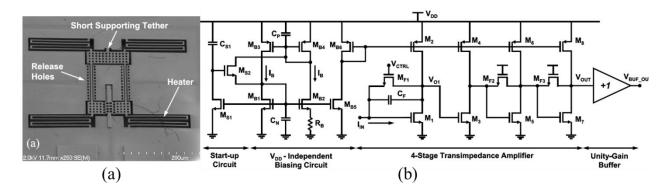

| Figure 1.7  | (a) A SEM image of the CMOS-MEMS resonator; b) schematic of a 4-stage transimpedance amplifier (TIA) with independent biasing circuit [21]                                                                                                                                                                                                                                                                                                                       | 9  |

| Figure 1.8  | (a) Output spectrum of the CMOS-MEMS oscillator; (b) phase noise performance of the CMOS-MEMS oscillator under two different biasing voltage of the resonator [21]                                                                                                                                                                                                                                                                                               | 9  |

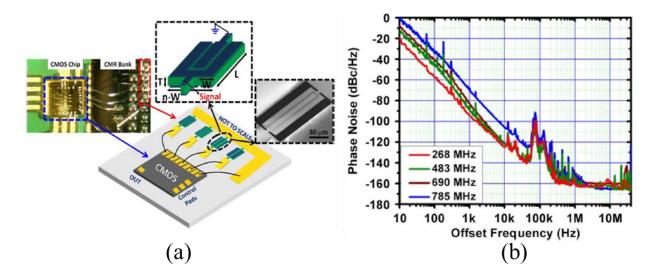

| Figure 1.9  | (a) Overview of the reconfigurable CMOS oscillator on a prototype<br>based on four-different-frequency AlN MEMS resonators, and<br>scanning-electron-microscope (SEM) of the resonator; (b) phase noise<br>performance of the reconfigurable CMOS oscillator                                                                                                                                                                                                     | 10 |

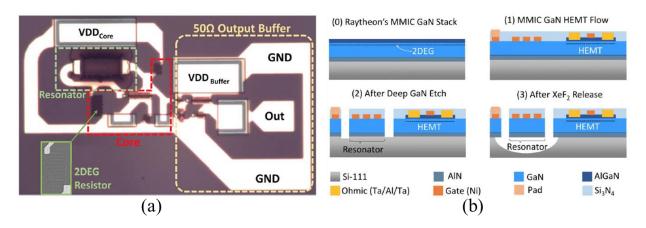

| Figure 1.10 | (a) Overview of the GaN-MEMS oscillator; (b) an Au-free modified MMIC HEMT process for GaN-MEMS resonators [24]                                                                                                                                                                                                                                                                                                                                                  | 11 |

| 16 |

|----|

| 17 |

| 20 |

| 21 |

| 22 |

| 24 |

| 25 |

| 28 |

| 31 |

| 33 |

| 34 |

|    |

v

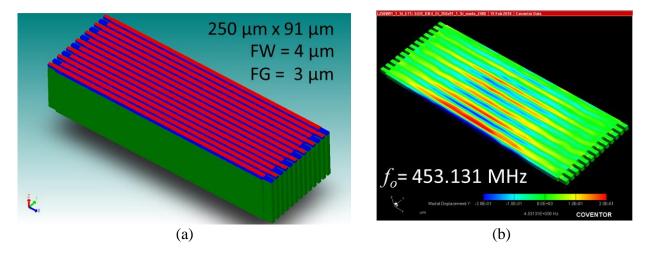

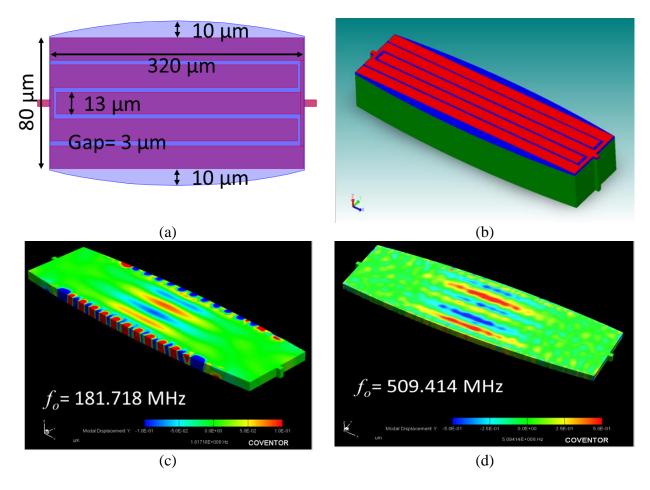

| Figure 3.4  | (a) A ZnO thin-film piezoelectric rectangular resonator on Diamond-on-<br>Si with 10 $\mu$ m wide curvature body that has a body dimension of 320<br>$\mu$ m x 80 $\mu$ m, finger number of 5, finger pitch size of 16 $\mu$ m, finger<br>width of 13 $\mu$ m and 1 pair of tethers; (b) 3-D view of the resonator in<br>CoventorWare; (c) modal displacement in Y direction of the 2 <sup>nd</sup> order<br>width-extensional (WE) mode; (d) modal displacement in Y direction<br>of the 3 <sup>rd</sup> order WE mode | 35 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

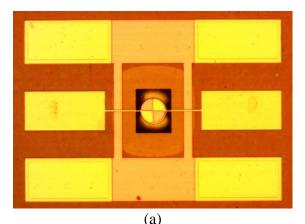

| Figure 3.5  | (a) Actual photograph of a two-port two-tether 30 $\mu$ m radius disk resonator fabricated on a SOI wafer with 10 $\mu$ m thick silicon device layer; (b) zoom-in view of a 30 $\mu$ m radius disk resonator with the fourtether design                                                                                                                                                                                                                                                                                 | 37 |

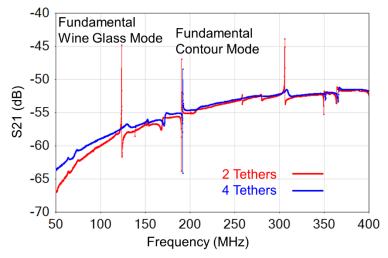

| Figure 3.6  | Measured frequency response (S <sub>21</sub> in dB) of the 30 $\mu$ m radius disk resonators fabricated on a SOI wafer: 2-Tether Design vs. 4-Tether Design                                                                                                                                                                                                                                                                                                                                                             | 38 |

| Figure 3.7  | Measure frequency response ( $S_{21}$ in dB) of a 40 $\mu$ m radius disk resonator on SOI in fundamental Radial-Contour mode                                                                                                                                                                                                                                                                                                                                                                                            | 38 |

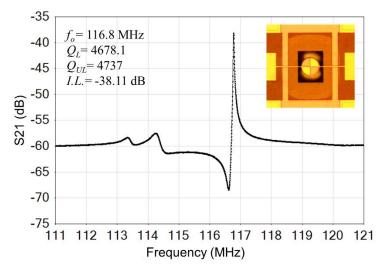

| Figure 3.8  | (a) Actual photograph of a ZnO thin-film piezoelectric rectangular resonator with curvature body on Diamond-on-Si that has a body dimension of 320 $\mu$ m x 80 $\mu$ m, finger number of 5, finger pitch size of 16 $\mu$ m, finger width of 13 $\mu$ m and 1 pair of tethers; (b) measured frequency response (S <sub>21</sub> in dB) of the resonator                                                                                                                                                                | 40 |

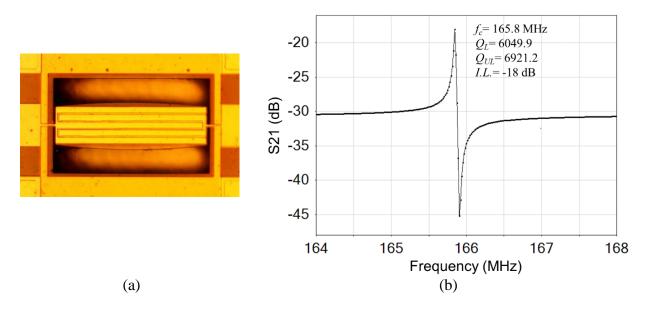

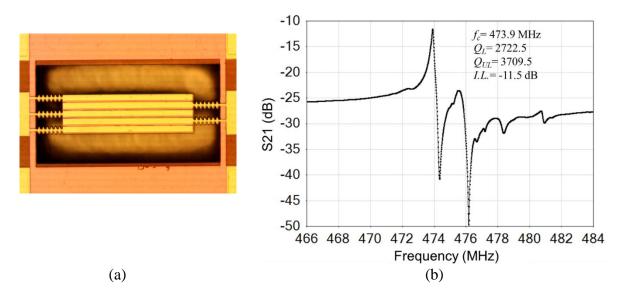

| Figure 3.9  | (a) Actual photograph of a ZnO thin-film piezoelectric rectangular resonator with curvature body on Diamond-on-Si that has 1 pair of Phononic Crystal (PC) strip tethers; (b) measured frequency response $(S_{21} \text{ in } dB)$ of the resonators with PC tether design and normal tether design                                                                                                                                                                                                                    | 41 |

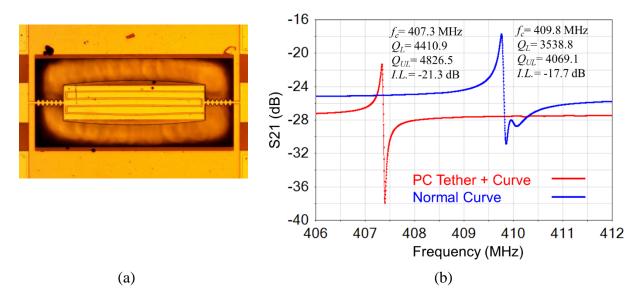

| Figure 3.10 | (a) Actual photograph of a ZnO thin-film piezoelectric rectangular resonator on Diamond-on-Si that has 5 Phononic Crystal (PC) strip tethers; (b) measured frequency response ( $S_{21}$ in dB) of the resonator                                                                                                                                                                                                                                                                                                        | 41 |

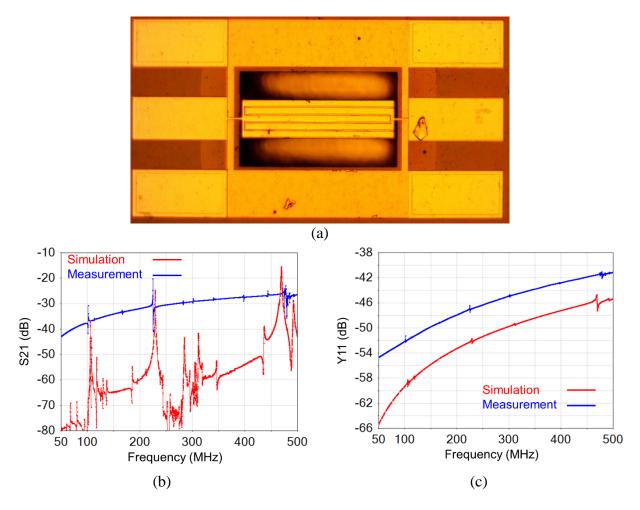

| Figure 3.11 | (a) Actual photograph of a ZnO thin-film piezoelectric rectangular resonator on Diamond-on-Si that has a body dimension of 320 $\mu$ m x 80 $\mu$ m, finger number of 5, finger pitch size of 16 $\mu$ m, finger width of 13 $\mu$ m and 1 pair of tethers; (b) measured and simulated frequency response (S <sub>21</sub> in dB) of the resonator; (c) measured and simulated frequency response (Y <sub>11</sub> in dB) of the resonator                                                                              | 43 |

|             | simulated frequency response (111 m db) of the resonator                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15 |

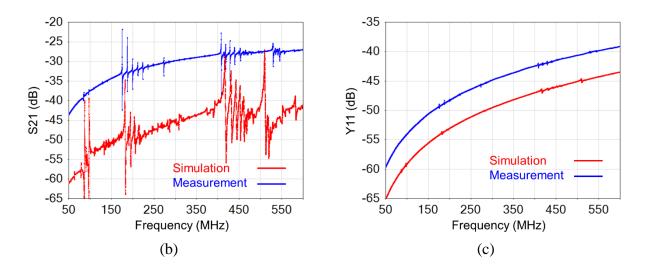

| Figure 3.12 | (a) measured and simulated frequency response ( $S_{21}$ in dB) of a 320 $\mu$ m x 80 $\mu$ m curvature resonator on Diamond-on-Si shown in Figure 3.8 (a); (b) measured and simulated frequency response ( $Y_{11}$ in dB) of the resonator                                                                                                                                                                                                                   | 44 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

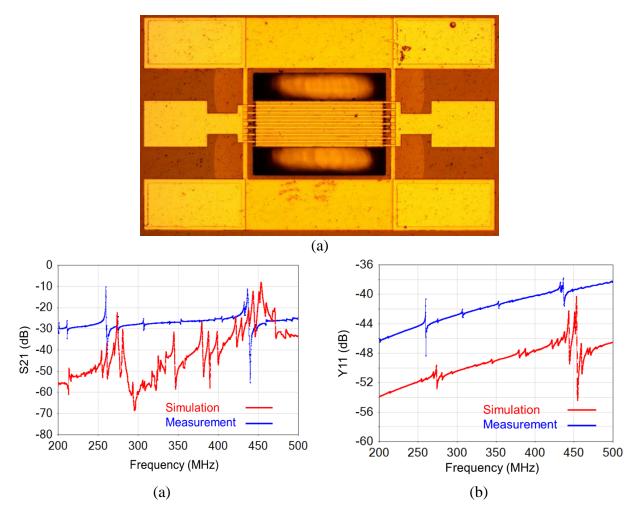

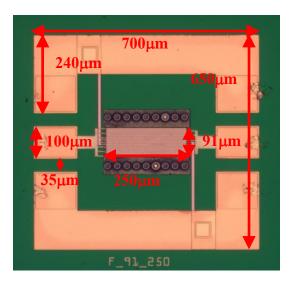

| Figure 3.13 | (a) Actual photograph of a ZnO thin-film piezoelectric rectangular resonator on SOI with a body dimension of 250 $\mu$ m x 91 $\mu$ m, finger number of 13, finger pitch size of 7 $\mu$ m, finger width of 4um and 13 tethers; (b) measured and simulated response (S <sub>21</sub> in dB) the resonator; (c) measured and simulated response (Y <sub>11</sub> in dB) the resonator                                                                           | 45 |

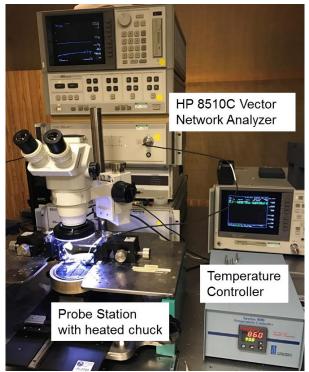

| Figure 3.14 | Setup for S-parameter measurement over temperature                                                                                                                                                                                                                                                                                                                                                                                                             | 48 |

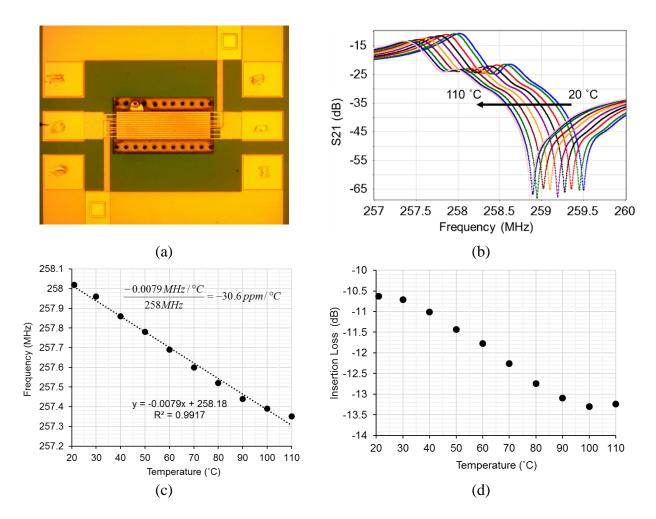

| Figure 3.15 | (a) A ZnO thin-film piezoelectric rectangular resonator on SOI with its body dimension of $300 \ \mu m \ x \ 91 \ \mu m$ , finger number of 13, finger pitch size of 7 $\mu m$ , finger width of 4um and 13 pairs of tethers; (b) measured frequency response of the resonator over a temperature range from 20 to $110^{\circ}$ C; (c) measured resonance frequency over temperature; (d) measured insertion loss of the resonance over temperature           | 49 |

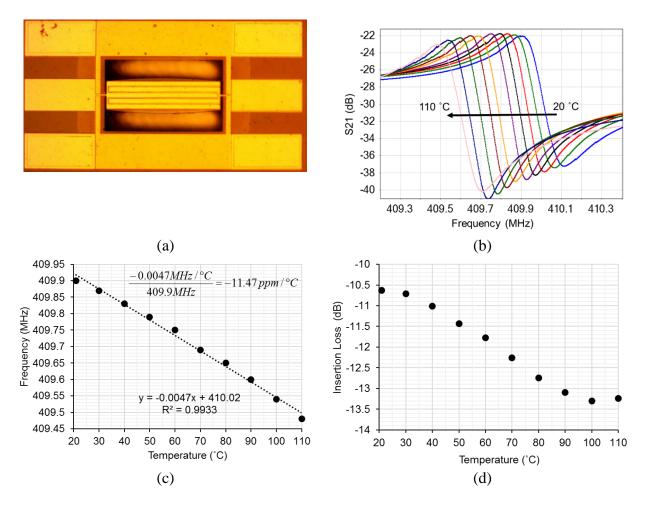

| Figure 3.16 | a) A photograph of ZnO thin-film piezoelectric rectangular resonator on Diamond-on-Si with its body dimension of 320 $\mu$ m x 80 $\mu$ m, finger number of 5, finger pitch size of 16 $\mu$ m, finger width of 13 $\mu$ m and 1 pair of tethers; (b) measured frequency response of the resonator over a temperature range from 20 to 110°C; (c) measured resonance frequency over temperature; (d) measured insertion loss of the resonance over temperature | 50 |

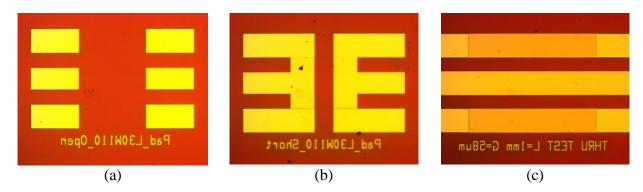

| Figure 3.17 | Actual photographs of fabricated de-embedding structures (a) Open;<br>(b) Short; and (c) Thru                                                                                                                                                                                                                                                                                                                                                                  | 52 |

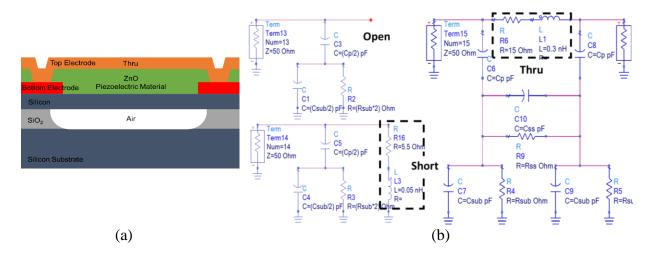

| Figure 3.18 | (a) Cross-sectional view of the Thru structure; (b) equivalent circuit model of three de-embedding structures: Open, Short and Thru                                                                                                                                                                                                                                                                                                                            | 52 |

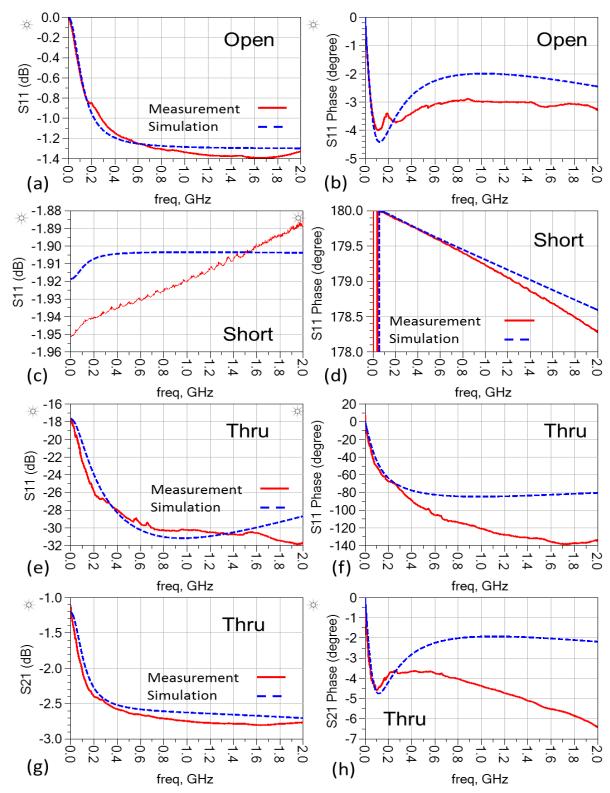

| Figure 3.19 | S-parameter results of measurement versus simulation on SOI: (a) $S_{11}$ magnitude of Open; (b) $S_{11}$ phase of Open; (c) $S_{11}$ magnitude of Short; (d) $S_{11}$ phase of Short; (e) $S_{11}$ magnitude of Thru; (f) $S_{11}$ phase of Thru; (g) $S_{21}$ magnitude of Thru; (h) $S_{21}$ phase of Thru                                                                                                                                                  | 55 |

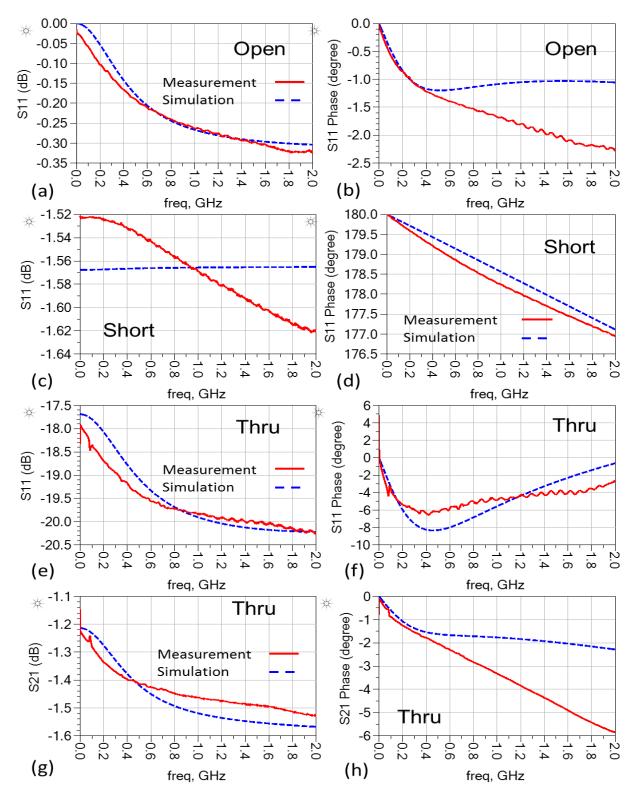

| Figure 3.20 | S-parameter results of measurement vs. simulation on DOS: (a) $S_{11}$ magnitude of Open; (b) $S_{11}$ phase of Open; (c) $S_{11}$ magnitude of Short; (d) $S_{11}$ phase of Short; (e) $S_{11}$ magnitude of Thru; (f) $S_{11}$ phase of Thru; (g) $S_{21}$ magnitude of Thru; (h) $S_{21}$ phase of Thru                                                                                                                                                     | 56 |

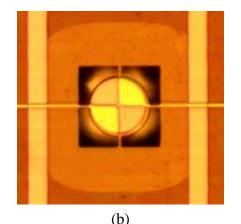

| Figure 4.1  | A top-view photo of a 250 $\mu$ m x 91 $\mu$ m ZnO-on-Si resonator along<br>with its key dimensions that is capable of operating in two width-<br>extensional modes                                                                                                                                                                                                                                 | 58 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.2  | An electrical equivalent circuit model for dual resonances of the ZnO-on-SOI resonator                                                                                                                                                                                                                                                                                                              | 60 |

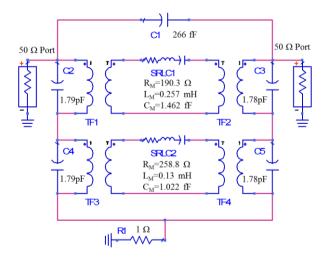

| Figure 4.3  | (a) A comparison between simulated and measured frequency<br>responses ( $S_{21}$ in dB) of the ZnO-on-SOI resonator; (b) a comparison<br>between simulated and measured frequency responses ( $S_{21}$ in phase)<br>of the ZnO-on-SOI resonator                                                                                                                                                    | 61 |

| Figure 4.4  | A typical MEMS based oscillator circuit diagram                                                                                                                                                                                                                                                                                                                                                     | 61 |

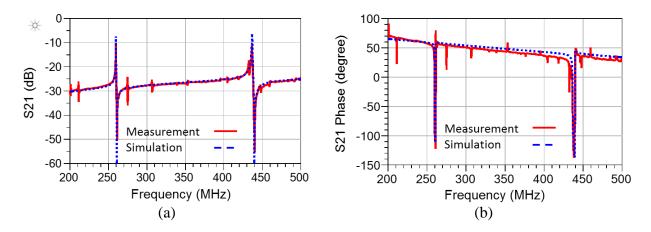

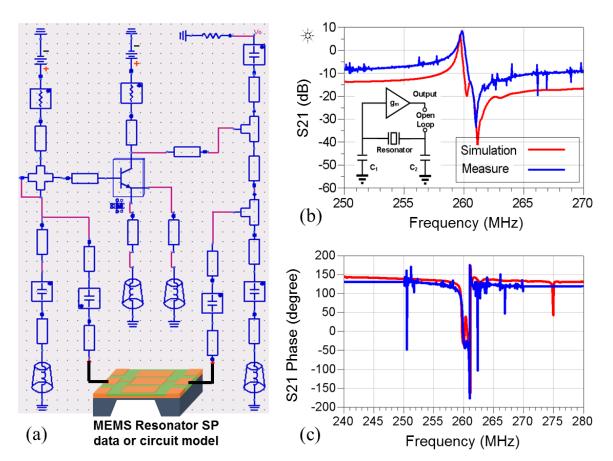

| Figure 4.5  | <ul> <li>(a) A complete Pierce oscillator circuit design simulated in ADS;</li> <li>(b) open-loop frequency response (S<sub>21</sub> in dB) of the resonator and sustaining amplifier circuit in ADS simulation and measurement;</li> <li>(c) open-loop frequency response (S<sub>21</sub> in phase) of the resonator and sustaining amplifier circuit in ADS simulation and measurement</li> </ul> | 63 |

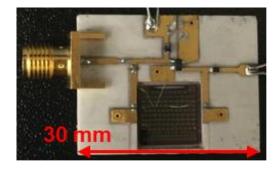

| Figure 4.6  | (a) Actual oscillator circuit milled on PCB with wire-bonded MEMS resonator; b) actual oscillator circuit milled on PCB circuit with coaxial connection to the MEMS resonator                                                                                                                                                                                                                       | 64 |

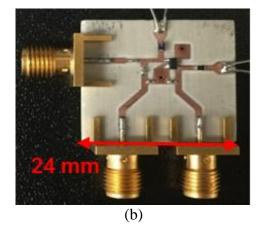

| Figure 4.7  | (a) Measured time-domain response using an oscilloscope; (b) comparison between measured data and two types of simulated time-domain output waveforms                                                                                                                                                                                                                                               | 64 |

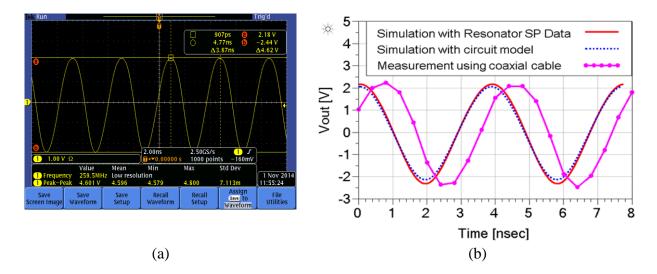

| Figure 4.8  | <ul> <li>(a) Measured frequency-domain response using a spectrum analyzer;</li> <li>(b) frequency spectrum of the oscillator locked to the resonant frequency of 437.5 MHz;</li> <li>(c) frequency spectrum of the oscillator locked to the resonant frequency of 259.5 MHz</li> </ul>                                                                                                              | 65 |

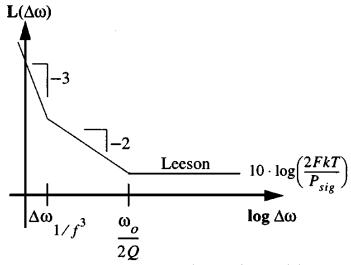

| Figure 4.9  | Leeson's phase noise model                                                                                                                                                                                                                                                                                                                                                                          | 66 |

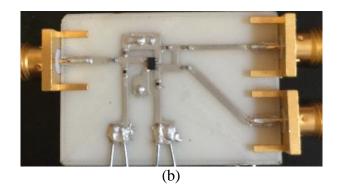

| Figure 4.10 | <ul><li>(a) A MEMS based common-emitter oscillator circuit milled on PCB;</li><li>(b) a 3-D printed MEMS based oscillator circuit</li></ul>                                                                                                                                                                                                                                                         | 67 |

| Figure 4.11 | The phase noise performance of all three oscillators at oscillation frequency of 260 MHz                                                                                                                                                                                                                                                                                                            | 68 |

| Figure 4.12 | The phase noise performance of all three oscillators at oscillation frequency of 430 MHz                                                                                                                                                                                                                                                                                                            | 69 |

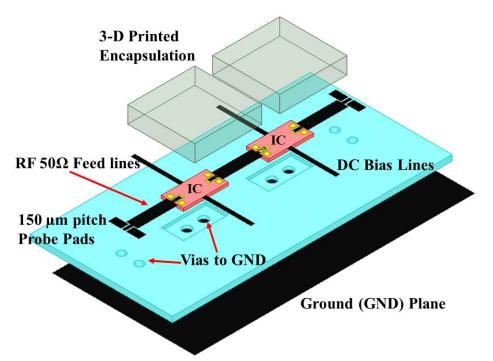

| Figure 5.1  | The overall view of the proposed 3-D printed hybrid package                                                                                                                                                                                                                                                                                                                                         | 72 |

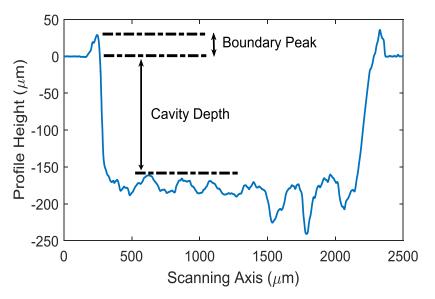

| Figure 5.2  | A cross-section profile of a laser machined cavity                                                                                                                                                                                                                                                                                    | 74 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 5.3  | The cavity profile with various average power levels                                                                                                                                                                                                                                                                                  | 74 |

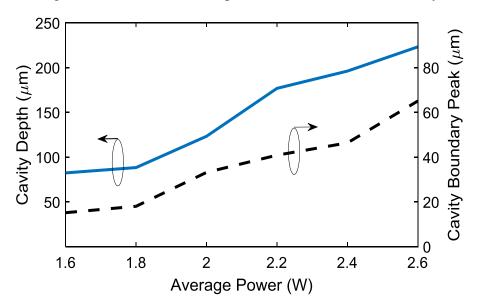

| Figure 5.4  | (a) A SEM image of a laser trimmed microstrip line; b) a SEM image<br>of a laser machined cavity; (c) a SEM image of a laser cut 150 $\mu$ m<br>pitch size probe pad; (d) a SEM picture of a close-up view of the laser<br>cut gap; (e) via holes of the probe pads for the ground connection;<br>(f) a hybrid packaging of a GaAs IC | 75 |

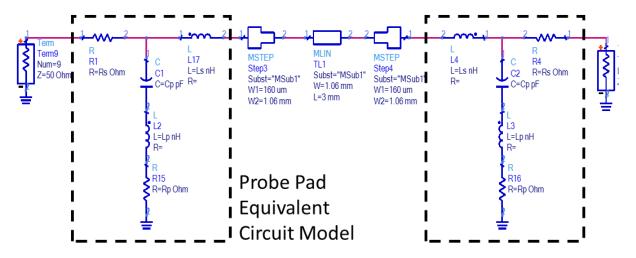

| Figure 5.5  | A probe pad equivalent circuit model and a full simulation of a 3-D printed 3 mm microstrip line                                                                                                                                                                                                                                      | 77 |

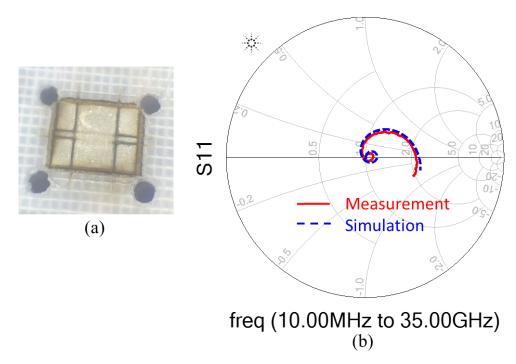

| Figure 5.6  | (a) A 3-D printed microstrip line and probe pads using laser machining;<br>(b) measured and simulated frequency response $S_{11}$ in Smith Chart of<br>a 3-D printed 3 mm microstrip line                                                                                                                                             | 77 |

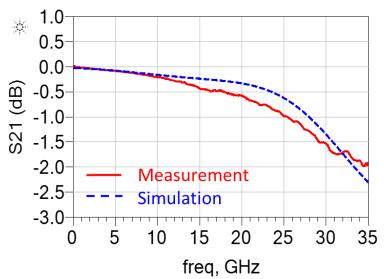

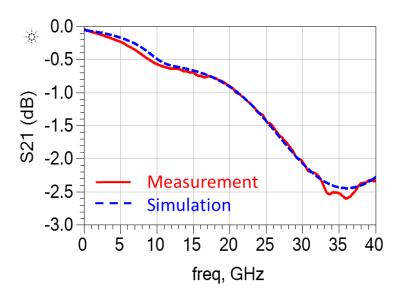

| Figure 5.7  | Measured and simulated frequency response $S_{21}$ in dB of a 3-D printed 3 mm long microstrip line                                                                                                                                                                                                                                   | 78 |

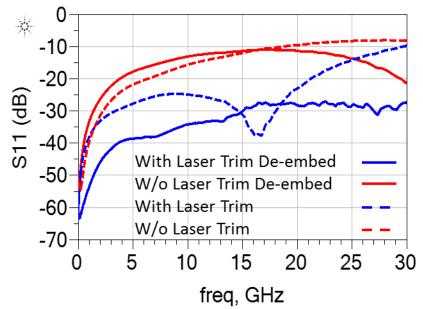

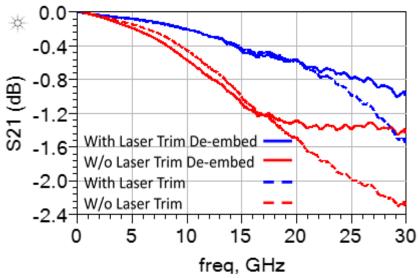

| Figure 5.8  | Measured frequency response $S_{11}$ in dB of a 3 mm microstrip line with laser trimming, without laser trimming, with laser trimming after de-embedding and without laser trimming after de-embedding                                                                                                                                | 79 |

| Figure 5.9  | Measured frequency response $S_{21}$ in dB of a 3 mm microstrip line<br>with laser trimming, without laser trimming, with laser trimming after<br>de-embedding and without laser trimming after de-embedding                                                                                                                          | 79 |

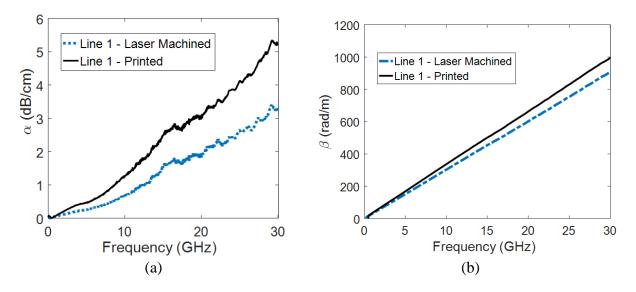

| Figure 5.10 | (a) Attenuation constant; and (b) phased constant of a 3 mm laser<br>trimmed microstrip line after de-embedding in comparison to a<br>microstrip line without laser trimming                                                                                                                                                          | 80 |

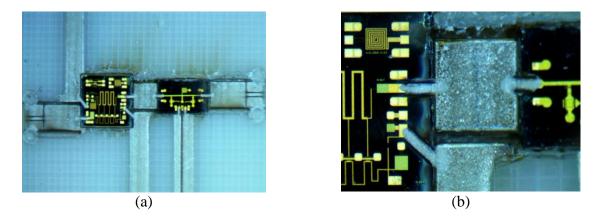

| Figure 5.11 | (a) Actual hybrid package of a GaAs distributed LNA and a GaAs active band-pass filter; (b) a close-up view of the transition and interconnects between ICs                                                                                                                                                                           | 82 |

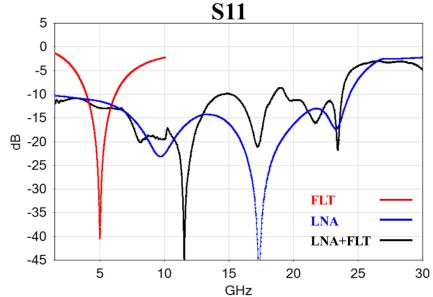

| Figure 5.12 | Measured frequency response $S_{11}$ in dB of a stand-alone filter, a stand-alone low-noise amplifier and both ICs in cascade                                                                                                                                                                                                         | 82 |

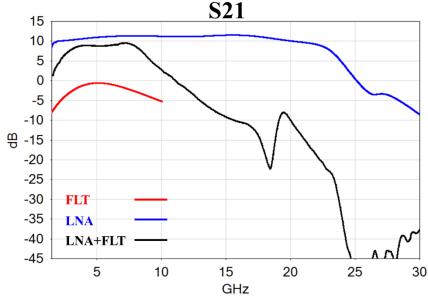

| Figure 5.13 | Measured frequency response $S_{21}$ in dB of a stand-alone filter, a stand-alone low-noise amplifier and both ICs in cascade                                                                                                                                                                                                         | 83 |

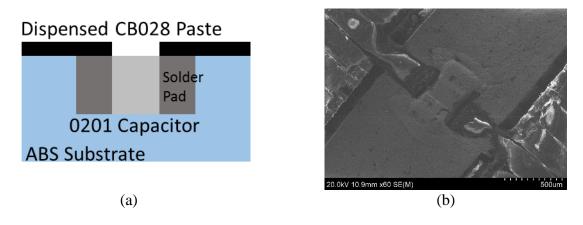

| Figure 5.14 | (a) A cross-section view of a SMT 0201 capacitor in the 3-D printed hybrid package; b) a SEM image of an integrated 0201 capacitor                                                                                                                                                                                                    | 84 |

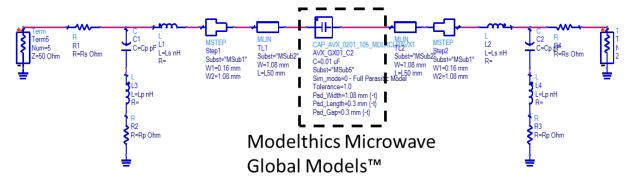

| Figure 5.15 | A full equivalent circuit model of the 3-D printed 0201 capacitor with probe pads                                                                                                                                                                                                     | 84  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

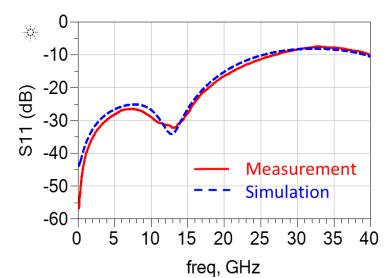

| Figure 5.16 | Measured and simulated frequency response $S_{11}$ in dB of the 3-D printed 0201 capacitor                                                                                                                                                                                            | 85  |

| Figure 5.17 | Measured and simulated frequency response $S_{21}$ in dB of the 3-D printed 0201 capacitor                                                                                                                                                                                            | 85  |

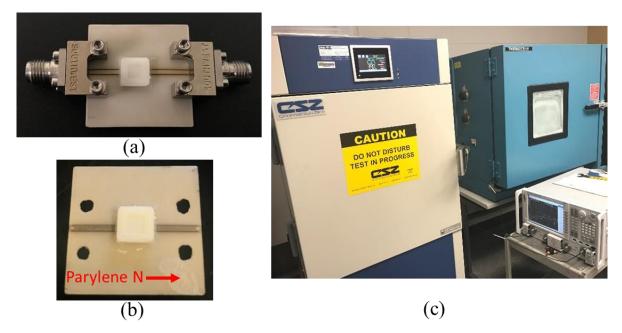

| Figure 5.18 | (a) A 3-D printed 50 $\Omega$ microstrip line with a hollow encapsulation<br>on top as a DUT for humidity and temperature cycling test; (b) the<br>DUT coated with Parylene N for water resist; (c) humidity and<br>temperature cycling test setup with an environmental test chamber | 07  |

|             | and a PNA                                                                                                                                                                                                                                                                             | 87  |

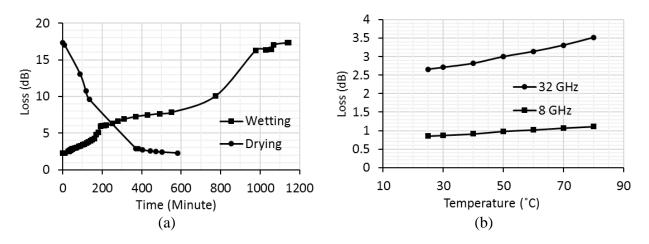

| Figure 5.19 | (a) Loss of the 3-D printed microstrip line over time during drying and wetting process; (b) loss of the 3-D printed microstrip line vs. temperature changing from 25 to 80 $^{\circ}$ C                                                                                              | 87  |

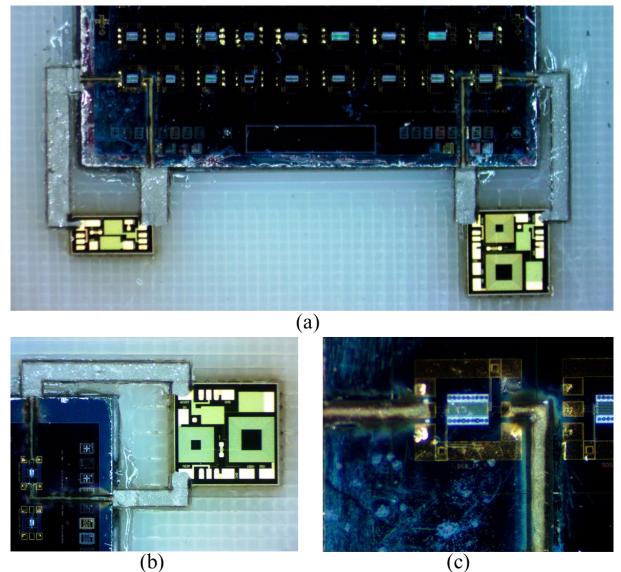

| Figure 6.1  | <ul> <li>(a) MEMS-based GaAs oscillators in 3-D printed hybrid packaging;</li> <li>(b) a zoom-in view of an integrated MEMS-based GaAs oscillator using 3-D printing;</li> <li>(c) 3-D printed interconnects from the signal pads of a resonator</li> </ul>                           | 91  |

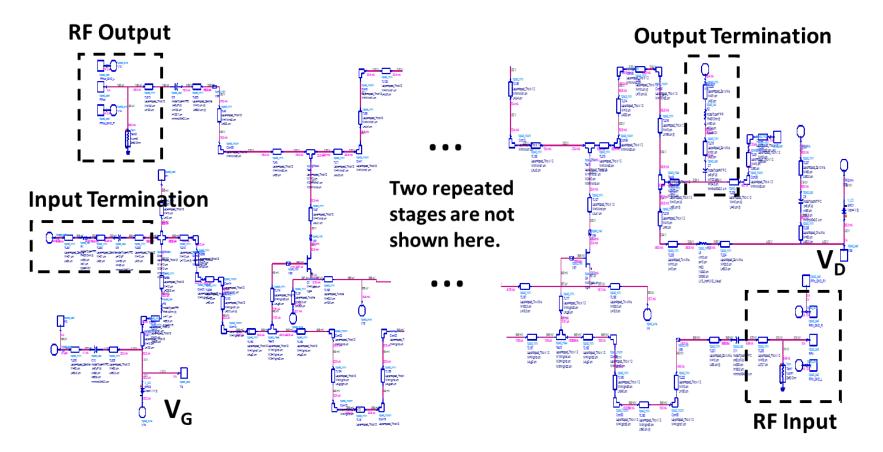

| Figure E.1  | Schematic of a 4-stage distributed low-noise amplifier                                                                                                                                                                                                                                | 117 |

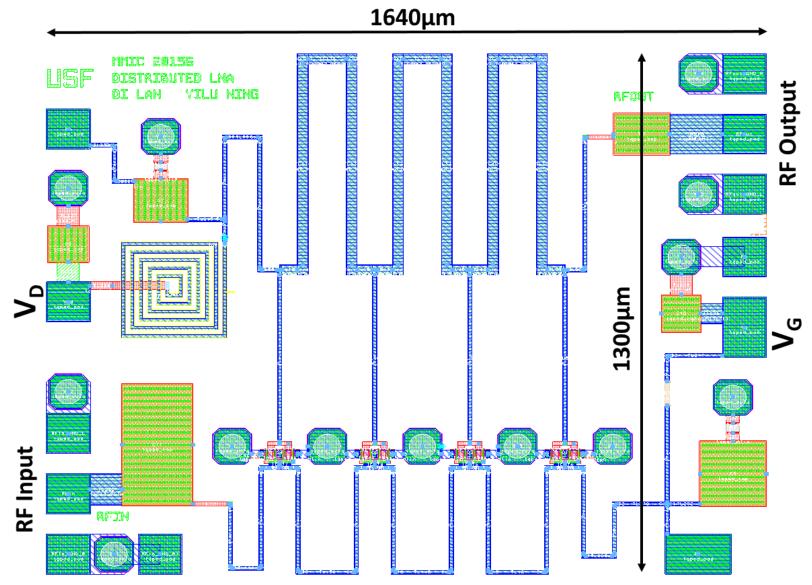

| Figure E.2  | Layout of a 4-stage distributed low-noise amplifier                                                                                                                                                                                                                                   | 118 |

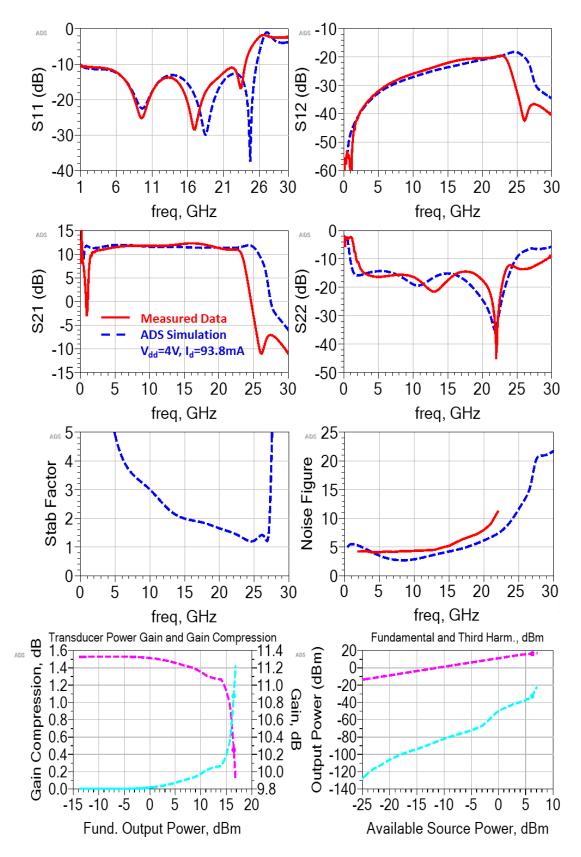

| Figure E.3  | Measured and simulated results of 4-stage distributed low-noise amplifier                                                                                                                                                                                                             | 119 |

## ABSTRACT

Prior research focused on CMOS-MEMS integrated oscillator has been done using various foundry compatible integration techniques. In order to compensate the integration compatibility, MEMS resonators built on standard CMOS foundry process could not take full advantage of highest achievable quality factor on chip. System-in-package (SiP) and system-on-chip (SoC) is becoming the next generation of electronic packaging due to the need of multi-functional devices and multi-sensor systems, thus wafer level hybrid integration becomes the key to enable the full assembly of dissimilar devices. In this way, every active circuit and passive component can be individually optimized, so do the MEMS resonators and sustaining amplifier circuits. In this dissertation, GaAs-MEMS integrated oscillator in a hybrid packaging has been fully explored as an important functional block in the RF transceiver systems.

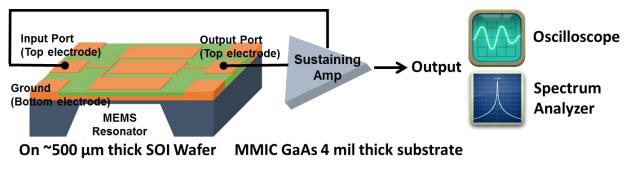

This dissertation first presents design, micro-fabrication, simulation, testing and modeling of ZnO piezoelectrically-transduced MEMS resonators. A newly designed rectangular plate with curved resonator body fabricated in-house exhibits a very high Q of more 6,000 in the air for its width-extensional mode resonance at 166 MHz. In addition, a rectangular plate resonator with multiple Phononic Crystal (PC) strip tethers shows low insertion loss of -11.5 dB at 473.9 MHz with a Q of 2722.5 in the air. An oscillator technology with high-Q MEMS resonator as its tank circuit is presented to validate its key functionality as a stable frequency reference across a wide spectrum of frequencies. Particularly, a piezoelectrically-transduced width-extensional mode mechanical modal frequencies (259.5MHz and 436.7MHz). These devices were characterized and modeled by

an extracted equivalent LCR circuit to facilitate the design of the oscillator using a standard circuit simulator. MEMS resonators have been integrated with the sustaining amplifier circuit at PCB level using wire-bonding technique and coaxial connectors. As shown by the time-domain measurements and frequency-domain measurements, these oscillators are capable of selectively locking into the resonance frequency of the tank circuit and generating a stable sinusoidal waveform. Meanwhile, the phase noise performance is rigorously investigated within a few oscillator designs. At last, 3-D printed hybrid packaging using additive manufacturing and laser machining technique has been developed for integrating a MEMS resonator on a silicon-on-insulator (SOI) substrate and a GaAs sustaining amplifier. Fabrication process and fundamental characterization of this hybrid packaging has been demonstrated. On-wafer probe measurements of a 50  $\Omega$  microstrip line on ABS substrate exhibit its insertion loss of 0.028 dB/mm at 5 GHz, 0.187 dB/mm at 20 GHz and 0.512 dB/mm at 30 GHz, and show satisfactory input and output return loss with the 3-D printed package. Parylene N is also experimentally coated on the package for improving water resistance as a form of hermetic packaging.

#### **CHAPTER 1: INTRODUCTION**

## **1.1 Overview**

Due to an explosive growth of personal mobile devices and ever-growing demand of multifunctional gadgets in the wireless communications, a great amount of research effort has been devoted to making present and future RF systems with lower size, weight, and power (SWaP) along with enriched functionalities and higher performance.

As a key enabler of the evolution of integrated wireless systems, Si CMOS technology continues to progress toward increasing functionality and complexity predicted by Moore's law with lower size, weight, and power (SWaP). Meanwhile, compound semiconductor III-V transistor devices and circuits have revolutionized RF electronics by offering superior frequency, gain, noise, and power characteristics at microwave and millimeter wave frequencies.

Despite the continuous success of the ever-growing IC industry fueled by Moore's law, the dependency on high quality factor on-chip passives is the key limiting factors against system-level miniaturization and integration. With the rapid development of MEMS technology for the past decade, it is now becoming a viable solution to batch-produce high-performance RF passive components, such as tunable filters, switches, capacitors, inductors and high-Q resonators for the next generation of wireless communication systems. Therefore, a convenient and parasitic-free heterogeneous integration of MEMS passives and III-V or Si CMOS transistor devices is required to create miniaturized, high-performance RF front-ends.

In modern wireless communications, an oscillator is an essential component of any wireless transceivers to provide performance-setting frequency references with high precision and low

noise. Traditionally, off-chip quartz crystal oscillators have been the most widely accepted choice despite its low level of integration with IC's and limited frequency range up to 100MHz. The advent of high-Q MEMS resonators has enabled the on-chip MEMS-based oscillators that can be fully integrated with on-chip transistor circuits, such as sustaining amplifiers, thus exhibiting a promising low phase noise at much higher frequencies than that of the quartz crystals.

Prior research towards development of on-chip frequency-setting passives has been focused on piezoelectrically-transduced contour-mode MEMS resonators, which do not require a polarization or bias voltage to operate and exhibit characteristic motional resistance typically lower than 1 k $\Omega$ . These two highly-unique advantages make the piezoelectrically-transduced contour-mode MEMS resonators a very promising alternative for implementation of oscillators at gigahertz frequencies.

Wafer level packaging is a promising solution for system-in-package (SiP) level of implementation of RF front end modules. In this work, seamless integration of high-Q MEMS resonator (array) and monolithic microwave integrated circuit through 3-D printed hybrid package using additive manufacturing and laser machining is going to be investigated to fulfill the stringent performance requirements for fully integrated reference oscillators.

#### **1.2 Review of MEMS Integration**

#### **1.2.1 CMOS-MEMS Integration**

Si CMOS as the most popular and promising technology exists inside every electronic device in our life. The recent advances in MEMS technology have become a promising enabler to yield RF modules and sub-systems with new functions. Consequently, RF MEMS devices have been successfully integrated with CMOS process with traditional hybrid approaches or advanced monolithic approach using similar or process compatible materials.

Figure 1.1 – A SEM image of a MEMS die wirebonded to a CMOS chip through a hybrid modular integration

The hybrid approaches of CMOS-MEMS integration as shown in Figure 1.1 are typically utilized by chip to wafer bonding (C2W), wafer to wafer bonding (W2W) and any other wafer stacking techniques [1]. This modular packaging method not only facilitates parallel work on individual design and optimization of MEMS devices and CMOS circuits, but also allows the maximum design freedom of MEMS and CMOS components. Therefore, hybrid approach has been widely employed on various products till today [2-4].

On the other hand, the monolithic approach has its key features against the hybrid approach, which are further miniaturization ability, low cost from single chip manufacturing and testing, and enhancement of signal to noise ratio due to parasitic reduction from shorter interconnects and its higher level of integration.

Within a single chip CMOS-MEMS development, monolithic integration can be realized through four main approaches: the pre-CMOS technology shown in Figure 1.2 (a); the intra-CMOS approach shown in Figure 1.2 (b); the post-CMOS technology shown in Figure 1.2 (c); and post-processing of CMOS-back end of line layers (BEOL) approach shown in Figure 1.2 (d) [5-8]. In

addition to great amount of integration development efforts required by all four monolithic approaches, they encounter different fabrication limitations and constraints such as MEMS layer thickness, thermal budget, and so on.

Figure 1.2 – Cross-sectional schematic diagrams of (a) an integrated CMOS-MEMS chip illustrating the well-known approach by Sandia National Lab [9]; (b) Infineon Technologies' integrated MEMS technology for the fabrication of pressure sensors [10]; (c) poly-SiGe microstructure fabricated by post-CMOS surface micromachining techniques on top of a completed CMOS substrate wafer [11]; and (d) a Nanomech MEMS embedded in the CMOS back end [12]

## 1.2.2 Wafer Level Packaging (WLP) and System in Package (SiP)

With the increasing demand for the miniaturized packages of multi-dies and multi-sensor devices in the high end electronics, wafer level packaging has been introduced as an innovative solution to accommodate all the manufacturing requirements. The main driving force, in terms of the performance metrics, for wafer level packaging is illustrated in Figure 1.3.

Figure 1.3 – Driving force for wafer level packaging [13]

Since "Fan-in" WLP as shown in Figure 1.4 (a) is typically limited to be less than 6mm x 6 mm in order to pass board level reliability requirements, "Fan-out" WLP has been invented for higher ball counts WLP and developed by extending the package area beyond the chip size as shown in in Figure 1.4 (b) [13]. Embedded wafer level ball grid array (eWLB) as the most prominent type of FO-WLP current available in industry was demonstrated by Infineon Technologies in 2008 [14]. The eWLB process starts with embedding a singulated die into an artificial wafer using a wafer level molding technique. And then metallization and isolation are applied on the die surface to fan-out the interconnections to the outside solder balls by standard wafer level lithography and patterning technique.

For side by side multichip eWLB packaging, additional number of interconnections between dies and dies to solder balls is significantly increased. Thus, redistribution layer (RDL) is

needed since it does not only yield higher performance electrical connection and complex routing using thin film technology, but also can provide embedded passive components using a multi-layer structure. Comparing to traditional wire bonding, RDL has fine pitch metallization and well-controlled interconnection with less parasitic. Low loss tall microstrip transmission lines (TMLs) in eWLB is fabricated and reported with insertion loss of 0.1 dB/mm @ 10GHz and 0.25 dB/mm @ 60GHz [15].

Figure 1.4 – Conceptual schematic diagrams illustrating (a) eWLB (FI-WLP); (b) eWLB (FO-WLP); (c) Package-on-package (PoP) using double-side eWLB packaging [13]; and (d) System-on-Wafer (SoW) using double-side eWLB packaging [16]

As eWLB applications are expanding to logic ICs, MEMS, III-V devices and discrete RF integration, 3-D eWLB approach such as PoP shown in Figure 1.4 (c) and SoW shown in Figure 1.4 (d) is critically needed for the miniaturization at sub-system and system level. It is gradually becoming a mainstream technology because of its flexibility of combining dissimilar materials and various technologies. However, due to the fact that 3-D eWLB is relied on through silicon vias (TSVs) to vertically connect the stacking chips, the quality of TSVs, which directly affects the

performance of the entire integration, is required to be fully characterized. Future study and research of interconnection and wiring are needed as well.

## 1.3 Current State of the Art MEMS-Based Oscillators

## **1.3.1 Monolithic CMOS-MEMS Oscillators**

Several fully monolithic MEMS-CMOS oscillators have been successfully demonstrated using process compatible materials with mature and well-developed complimentary metal-oxidesemiconductor (CMOS) foundry process. CMOS-MEMS vertically-coupled resonator and their associated on-chip transimpedance amplifiers in Figure 1.5 (b) are fabricated utilizing a standard TSMC 0.35  $\mu$ m CMOS technology from Sheng-Shian Li's group in 2015 [17]. This MEMS resonator shown in Figure 1.5 (a) consists of patterned metal electrodes (yellow) embedded inside the top thick oxide plate (green), bottom thin plate formed by polysilicon and oxide polysilicon and an oxide stem placed at the center. There are two vibration modes, which are saddle (SA) mode and vertically-coupled (VC) mode in this resonator. Because of the large capacitive transduction gap (>1  $\mu$ m) from the 0.35  $\mu$ m CMOS process, A DC bias voltage (~200 V) is required to actuate the resonator with the resultant motional resistance of 60 k $\Omega$ . Transmission response of the resonator plotted in Figure 1.6 (a) shows 6.5 MHz resonant frequency, 1,000 quality factor in vacuum (< 0.1 mTorr) for VC-Mode under 150 V DC biasing condition. Comparing to other prior reports of monolithically integrated oscillators [18-20], the best-case phase noise of the VC-mode oscillator shown in Figure 1.6 (b) with -97 dBc/Hz at 1-kHz and -118 dBc/Hz at 1-MHz offset from carrier respectively is slightly better.

7

Figure 1.5 - (a) Perspective view of the vertically-coupled resonator; (b) Optical photos of the CMOS-MEMS resonator oscillator [17]

Figure 1.6 - (a) Magnitude and phase responses of the proposed resonator; (b) Phase noise performance comparison [17]

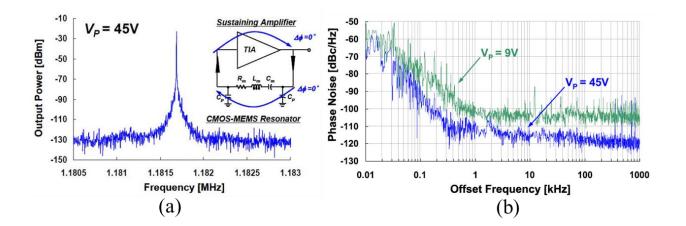

Another monolithic CMOS-MEMS oscillator shown in Figure 1.7 (a) using TSMC 0.35  $\mu$ m CMOS technology has also been reported in the same group [21]. The CMOS-MEMS resonator was released using chip level post-CMOS process without a mask layer. The resonator was characterized to have 700 k $\Omega$  motional resistance ( $R_M$ ) and quality factor up to 3,000 under a vacuum level of 100  $\mu$ Torr environment while biasing with 45 V. The quality factor (Q) of such resonator dramatically degrades to only 150 once it is operated under ambient pressure. Due to the extremely high  $R_M$ , a 4-stage transimpedance amplifier is designed in Figure 1.7 (b) to provide enough gain and bandwidth to sustain the oscillation at 1.2 MHz. The output spectrum of the oscillator is plotted in Figure 1.8 (a). While only consuming less than 1.3 Mw of power, this

monolithic CMOS-MEMS oscillator exhibits measured phase noise of -112 dBc/Hz at 1-kHz offset from the carrier, and -120 dBc/Hz at 1-MHz offset from carrier as shown in Figure 1.8 (b).

Figure 1.7 - (a) A SEM image of the CMOS-MEMS resonator; b) schematic of a 4-stage transimpedance amplifier (TIA) with independent biasing circuit [21]

Figure 1.8 - (a) Output spectrum of the CMOS-MEMS oscillator; (b) phase noise performance of the CMOS-MEMS oscillator under two different biasing voltages of the resonator [21]

## **1.3.2 Piezoelectric AlN-Based CMOS Oscillators**

In Piazza's group, they have done research on AlN Contour-Mode MEMS resonator based CMOS oscillators for years, especially focusing on reconfigurable CMOS oscillators for generation of multiple frequencies recently [22]. Four resonators with a quality factor of 1,750 to 3,000 are designed based on four sets of parameters, which are width, finger number, length and

AlN thickness, therefore resonance frequencies of 268 MHz, 483 MHz, 690 MHz and 785 MHz are generated from these oscillator tanks. AlN resonators, CMOS switches and COMS amplifiers using 0.5  $\mu$ m technology are integrated together on a printed circuit board (PCB) through wirebonding as shown in Figure 1.9 (a). Phase noise performance for these oscillators at the different frequency is plotted in Figure 1.9 (b) and the best one achieves -95 dBc/Hz at 1-kHz offset from carrier, and -160 dBc/Hz at 1-MHz.

Figure 1.9 - (a) Overview of the reconfigurable CMOS oscillator on prototype based on four-different-frequency AlN MEMS resonators, and scanning-electron-microscope (SEM) of the resonator; (b) phase noise performance of the reconfigurable CMOS oscillator

Instead of using multiple resonator tank for various frequency references, a single AlN-on-Si MEMS oscillator has also been demonstrated under its dual-frequency operation using first/third (35.5/105.7 MHz) order modes of the MEMS resonator [23]. A switching network circuit is incorporated into transimpedance amplifier circuit design so that the oscillation frequency changes with different phase shift. The measured phase noise for both frequencies is around -110 dBc/Hz at 1 kHz offset from carrier and -140 dBc/Hz 1MHz offset from carrier.

## 1.3.3 MEMS-Based GaN Oscillators

Recently, a 1 GHz monolithically integrated GaN-MMIC oscillator shown in Figure 1.10 (a) has been realized using GaN-on Si heterostructure from Raytheon [24]. The Lamb mode GaN resonator is side by side with the rest of circuits and released from a deep trench etch followed by a silicon etch as shown in Figure 1.10 (b). Fabricated resonator has 390 $\Omega$  motional resistance and a quality factor of 4,250 while it is measured under a vacuum level of 10<sup>-5</sup> Bar. The phase noise performance of this GaN-MEMS oscillator exhibits phase noise of -82 dBc/Hz at 1 kHz offset from carrier and -130 dBc/Hz 1MHz offset from carrier. This oscillator only occupied 268 x 214  $\mu$ m<sup>2</sup> area on the chip which is 10 times smaller than the FBAR oscillator [25].

Figure 1.10 – (a) Overview of the GaN-MEMS oscillator; (b) an Au-free modified MMIC HEMT process for GaN-MEMS resonators [24]

## 1.3.4 Drawbacks of the Current State-of-the-Art Technology

• Despite the fact that MEMS resonator fabricated with CMOS compatible technology is monolithically integrated to the rest of the circuit, the oscillator is still required to operate under vacuum condition while exhibiting low oscillation frequency. Due to the extremely high motional resistance of the CMOS-MEMS resonator even at relatively low frequencies, very complex performance-demanding multi-stage transimpedance amplifier circuit design is often required which causes longer design cycle and a bit higher power consumption.

- AlN resonator exhibits high resonance frequency and reasonable quality factor of less than 3,000 in air. However, wirebonded oscillator not only limits the best achievable performance but also hinders future miniaturization.

- Although newly developed GaN-MEMS oscillator has decent performance and tiny size because of its monolithic integration, it still requires vacuum level package and highly specialized GaN process. After all, GaN does not offer comparable piezoelectric coefficient on par with that of AlN, ZnO, etc.

## **1.4 Dissertation Organization**

This dissertation is organized into six chapters and three appendices. Chapter 1, as an introductory chapter, first presents an overview and motivation of this dissertation work. And then it focus on reviewing current MEMS integration technology and current state of the art MEMS based oscillator design. The main goals and contributions of this dissertation are also described at the end of this chapter.

In Chapter 2, fundamental knowledge and basic mathematic formula of piezoelectricity are provided. In addition, this chapter presents the equivalent mechanical domain and electrical domain representation of a MEMS resonator, especially Butterworth-Van Dyke (BVD) circuit model as an extended analysis of the electrical model. Detailed fabrication processes for ZnO piezoelectric MEMS resonators on Silicon-on-insulator and Diamond-on-Silicon wafer are described in Chapter 3, followed by the comparison between measured and simulated results of micro-fabricated devices. Substrate model including probe pad and microstrip line is analyzed and discussed in this chapter as well. Chapter 4 presents the design and implementation of MEMS based oscillators using a ZnO piezoelectric resonators using different transistor technology and fabrication methods. In Chapter 5, a novel 3-D hybrid package using additive manufacturing and

laser machining is introduced and the fabrication process is described in detail. The integration of multiple ICs on a 3-D printed substrate is demonstrated along with the analysis of its performance.

Chapter 6 concludes the findings of this work while also providing the viable directions for future research work.

## **1.5 Contributions**

In this work, ZnO piezoelectrically-transduced resonators have been designed, fabricated and demonstrated with high-Q and high-frequency that is one of the main contributions of this dissertation work. The layout for the 5-mask fabrication process is drawn via CAD tool. Various designs (e.g., curved resonator body, Phononic Crystal strip tethers, and acoustic reflector) of the width-extensional mode resonators are designed for high-Q and low insertion loss devices. Proposed fabrication processes for the resonator on SOI and diamond-on-silicon (DOS) have been successfully implemented at the cleanroom facility at USF. Those micro-fabricated resonators are intensively characterized through measurement and simulation. Suitable ones are selected as resonator tanks for the oscillator design.

To facilitate the oscillator design and circuit analysis for a complete reference oscillator circuit simulation, electrical equivalent circuit model of the piezoelectrically-transduced resonator has been developed and experimentally verified. Measured frequency response of the resonator are compared with simulation results for additional validation. The sustaining amplifier circuits are designed based on the characteristics of the fabricated resonators for the oscillator design. MEMS resonators operating at 260 MHz and 430 MHz are integrated with the sustaining amplifier circuit using wire-bonding technique and coaxial connectors. Thus, the second main contribution is the implementation of a dual-frequency MEMS based oscillator using a single ZnO-on-SOI

resonator which is published in [57]. The phase noise performance for those oscillators have been rigorously measured and analyzed, which is largely on par with those of the prior works.

Gallium arsenide (GaAs) high-electron-mobility-transistor (HEMT) is one of the III-V direct bandgap semiconductor technologies that allows the monolithic integrated circuits (MMIC) to operate at very high frequencies with low noise figure, due to its high electron mobility and excellent noise parameters. Superior properties of GaAs make it widely used in microwave and RF circuities, and an excellent candidate for oscillator circuit using in RF systems. Hence, the sustaining amplifiers for oscillator design using the GaAs HEMT technology have been designed and implemented for the future chip-level integration. To further understand GaAs HEMT technology from the complementary foundry service from TriQuint Semiconductor Inc., a 2-22 GHz distributed low-noise amplifier (LNA) is designed and taped out as the third main contribution. The S-parameters of the LNA along with its noise figure are measured and compared with the simulation results. Also, this chip is used for development of the hybrid package.

The primary goal of this work is to develop a generic hybrid integration methodology for a MEMS resonator and GaAs MMIC to offer ease of manufacturing, individual optimization of circuitries, reduction of design cycle, and low-level parastics along with a better SWaP. Therefore, 3-D printed interconnects and hybrid package for integration of multiple IC chips using additive manufacturing and laser machining have been successfully developed and demonstrated for the first time.

14

#### **CHAPTER 2: BACKGROUND**

## **2.1 Piezoelectric Effect**

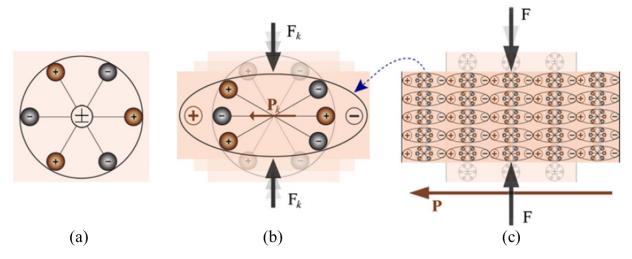

Piezoelectric effect was first discovered by Pierre and Jacques Curie in 1881. They demonstrated that mechanical stresses from external pressure in certain materials such as topaz, zinc blende, and quartz can generate electric charges. Piezoelectric effect describes a link between electrostatics and mechanics and it is normally understood as the linear electromechanical interaction between the mechanical and the electrical state in crystalline materials with no inversion symmetry [26]. The piezoelectric effect can be simply explained by a molecular model shown in Figure 2.1. In Figure 2.1 (a), a molecule that has 3 negative and positive charges is electrically neutral without subjecting an external force. However, when the molecule is deformed with an external mechanical stress as shown in Figure 2.1 (b), a dipole is created by the separation of the positive and negative around the center position. As a result, the positive and negative charges facing each other inside the material are canceled and then the material is polarized with the fixed charges on the surface shown in Figure 2.1(c). This phenomenon is called direct piezoelectric effect. Piezoelectric materials can generate and accumulate an electrical charge from an applied mechanical force. The amount of charge generated is directly proportional to the applied mechanical stress strength. Vice versa, a reverse piezoelectric effect also exists because piezoelectricity is a reversible and bi-directional energy conversion mechanism. A mechanical deformation results in a piezoelectric material when an electrical field is applied.

15

Figure 2.1 – A simple molecular model of piezoelectric effect: (a) an unperturbed molecule with no piezoelectric polarization (though prior electric polarization may exist); (b) The molecule subjected to an external force ( $F_k$ ), resulting into polarization ( $P_k$ ) as indicated; (c) The polarizing effect on the surface when piezoelectric material is subjected to an external force [27]

#### 2.2 Mathematical Formation for Piezoelectric Effect

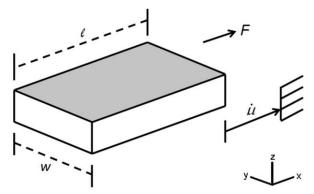

The piezoelectric effect in practice results in a cross-coupling between the electrical and mechanical behavior of a material. Since piezoelectric materials are anisotropic, their physical properties (e.g., permittivity, elasticity, and piezoelectric constant) are tensor quantities. Base on the linear theory of piezoelectricity [28], the equations that describe the relationship between mechanical stress (T), mechanical strain (S), an electrical field (E) and electrical displacement (D) are given as:

$$S_P = s_{pq}^E T_q + d_{pk} E_k \tag{2.1}$$

$$D_i = d_{iq}T_q + \varepsilon_{ik}^T E_k \tag{2.2}$$

where  $S_p$  is the mechanical strain in the *p* direction,  $s_{pq}^{E}$  is elastic compliance under constant electric field,  $T_q$  is mechanical stress in the *q* direction,  $d_{kp}$  is piezoelectric constant,  $E_k$  is the electric field in the *k* direction,  $\varepsilon_{ik}^{T}$  is dielectric constant tensor under constant stress, and  $D_i$  is electric displacement in the *i* direction. Those constants are expressed with two subscript indices.

The first subscript index defines the axis of the excitation and the second one refer to the actuation orientation.

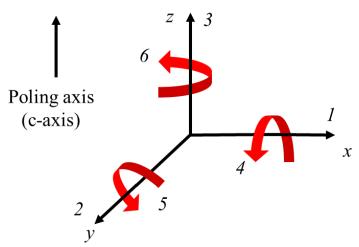

Figure 2.2 – Tensor directions for defining piezoelectricity

The crystallographic axes depicted in Figure 2.2 are defined using the notation of a Cartesian rectangular system. Original directions of x, y, and z are represented by 1, 2, and 3, respectively, whereas the shear planes are labeled as 4, 5, and 6, respectively. Usually, the direction of positive polarization is chosen to coincide with the z-axis.

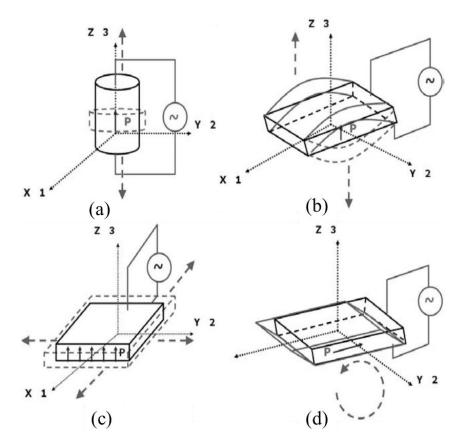

Four alternate forms explain the electromechanical coupling from different perspectives are listed below.

The stress-charge form is expressed as:

$$T_{6\times1} = c_{6\times6}^E \cdot S_{6\times1} + e_{6\times3} \cdot E_{3\times1}$$

$$D_{3\times1} = e_{3\times6} \cdot S_{6\times1} + \varepsilon_{3\times3}^S \cdot E_{3\times1}$$

(2.3)

The strain-charge form is expressed as:

$$S_{6\times 1} = s_{6\times 6}^E \cdot T_{6\times 1} + d_{6\times 3} \cdot E_{3\times 1}$$

$$D_{3\times 1} = d_{3\times 6} \cdot T_{6\times 1} + \varepsilon_{3\times 3}^T \cdot E_{3\times 1}$$

(2.4)

The strain-voltage form is expressed as:

$$S_{6\times 1} = s_{6\times 6}^{D} \cdot T_{6\times 1} + g_{6\times 3} \cdot D_{3\times 1}$$

$$E_{3\times 1} = -g_{3\times 6} \cdot T_{6\times 1} + \beta_{3\times 3}^{T} \cdot D_{3\times 1}$$

(2.5)

The stress-voltage form is expressed as:

$$T_{6\times 1} = c_{6\times 6}^{D} \cdot S_{6\times 1} - h_{6\times 3} \cdot D_{3\times 1}$$

$$E_{3\times 1} = -h_{3\times 6} \cdot S_{6\times 1} - \beta_{3\times 3}^{S} \cdot D_{3\times 1}$$

(2.6)

where *c* is the stiffness matrix and *e* is the piezoelectric constant matrix.  $\beta$  is the inverse matrix of permittivity, and *d*, *g*, and *h* are the alternate forms of piezoelectric constants.

## **2.3 Piezoelectric Materials**

Piezoelectric crystals and piezoelectric ceramics are two major categories of piezoelectric materials. Quartz as the most well-known piezoelectric material is a natural piezoelectric crystal that is widely used in piezoelectric filters, timing and frequency reference devices such as oscillators for a few decades because of its mechanical strength, small dielectric loss, chemically stability and low thermal coefficient expansion, which translates to an excellent dimensional stability under temperature variations. Although it has such desirable characteristics, the practical frequency limitation for a fundamental mode AT-cut crystal is around 30 MHz [29].

Meanwhile, there are several also excellent ceramic materials that exhibit piezoelectric behavior and are most widely used in transducers and MEMS applications such as aluminum nitride (AlN), zinc oxide (ZnO), barium titanate (BaTiO<sub>3</sub>) and lead-zirconate-titanate (PZT). Although BaTiO<sub>3</sub> has a very high piezoelectric strain coefficient  $d_{31}$  of -58 which is more than 10 times higher than AlN and ZnO, its high thermal expansion coefficient and low Curie point limit itself for further development. Similar to BaTiO<sub>3</sub>, PZT also has extremely high electromechanical coupling coefficient. However, process compatibility of PZT prevents itself from being widely

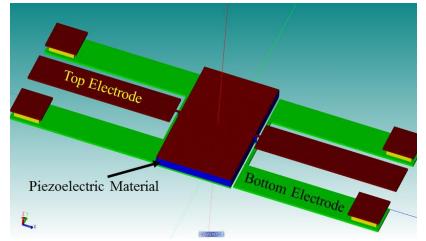

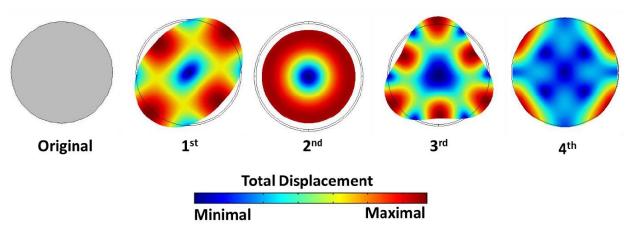

used with many CMOS technologies due to the fact PZT contains the lead element. Since highquality AlN and ZnO films can be easily obtained by sputtering at a relatively low temperature (below 400 °C) to offer compatibility with CMOS processing, AlN and ZnO become the most widely used piezoelectric thin film material in MEMS applications. Furthermore, the low processing temperatures of these materials also enable post-CMOS integration process while retaining aluminum as the metallization layer. Table 2.1 summarizes the properties of these materials mentioned above.